PhD Student @ UMich CSE

PhD Student @ UMich CSEMy name is Leonard Zhang and I am a first-year PhD student at EECS Department at University of Michigan, Ann Arbor, working with Professor Ke Sun at AmI lab.

My research focuses on developing novel and efficient intelligent embedded and sensing systems. Mobile and embedded AI systems always face challenges such as constrained computations, scarce energy availability, limited communication bandwidth, and the requirements for reliable long-term operation. I aim to create practical solutions that prioritize efficiency, sustainability, and user accessibility of mobile sensing systems, while supporting diverse backend machine learning applications.

My recent projects include building novel sensing systems on smartglasses for daily memory augmentations and efficient collaborative learning over LPWANs ORCA [SenSys'25]. My previous research mainly relates to build efficient machine learning frameworks on resource-constrained embedded systems: E-QUARTIC [ASP-DAC'25], Antler [EWSN'24], and Capuchin [IPSN'22].

Meanwhile, I am closely working with my furry research partner Miss Hope, an adopted American domestic shorthair raised in the Midwest. My research primarily focuses on how to efficiently interact and negotiate with her from tampering with my jumper wires and sleeping on my keyboard.

Warning

Problem: The current name of your GitHub Pages repository ("Solution: Please consider renaming the repository to "

http://".

However, if the current repository name is intended, you can ignore this message by removing "{% include widgets/debug_repo_name.html %}" in index.html.

Action required

Problem: The current root path of this site is "baseurl ("_config.yml.

Solution: Please set the

baseurl in _config.yml to "Education

-

University of Michigan, Ann ArborElectrical Engineering and Computer Science Department

University of Michigan, Ann ArborElectrical Engineering and Computer Science Department

Ph.D. Student in Computer Science and EngineeringStarting Sep. 2025 -

University of California, San DiegoDepartment of Computer Science and Engineering

University of California, San DiegoDepartment of Computer Science and Engineering

M.S. in Computer ScienceSep. 2023 - Jun. 2025 -

University of North Carolina at Chapel HillB.A. in Computer ScienceAug. 2019 - Dec. 2022

University of North Carolina at Chapel HillB.A. in Computer ScienceAug. 2019 - Dec. 2022

Selected Publications (view all )

Offload Rethinking by Cloud Assistance for Efficient Environmental Sound Recognition on LPWANs

Le Zhang*, Quanling Zhao*, Run Wang, Shirley Bian, Onat Gungor, Flavio Ponzina, Tajana Rosing (* equal contribution)

the ACM Conference on Embedded Networked Sensor Systems (SenSys) 2025

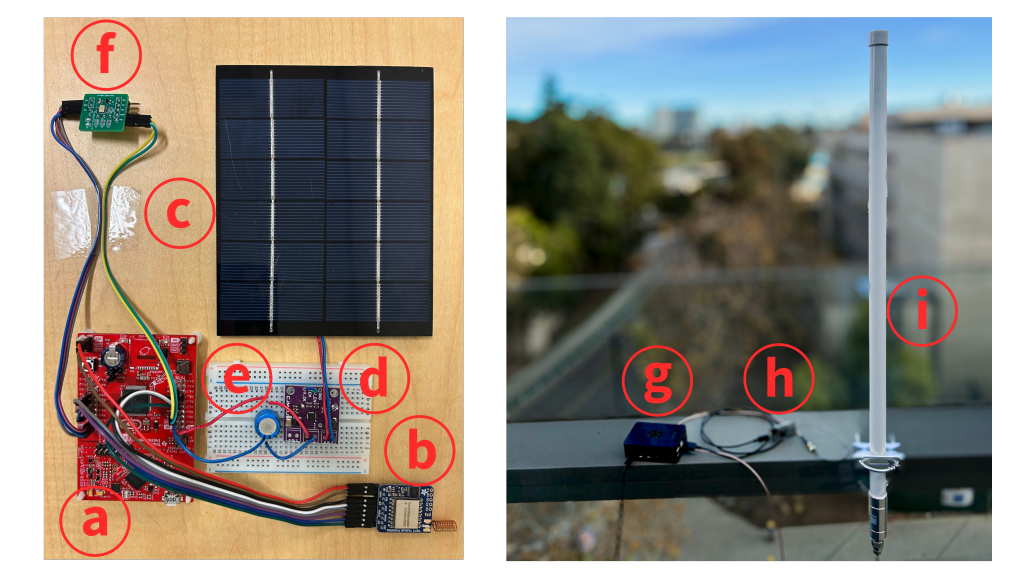

We present ORCA, a resource-efficient, cloud-assisted environmental sound recognition system designed for batteryless devices using Low-Power Wide-Area Networks (LPWANs). ORCA addresses the accuracy limitations of on-device methods and reduces communication costs of cloud-offloading strategies, enabling ultra-low-power, wide-area audio sensing applications.

Offload Rethinking by Cloud Assistance for Efficient Environmental Sound Recognition on LPWANs

Le Zhang*, Quanling Zhao*, Run Wang, Shirley Bian, Onat Gungor, Flavio Ponzina, Tajana Rosing (* equal contribution)

the ACM Conference on Embedded Networked Sensor Systems (SenSys) 2025

We present ORCA, a resource-efficient, cloud-assisted environmental sound recognition system designed for batteryless devices using Low-Power Wide-Area Networks (LPWANs). ORCA addresses the accuracy limitations of on-device methods and reduces communication costs of cloud-offloading strategies, enabling ultra-low-power, wide-area audio sensing applications.

E-QUARTIC: Energy Efficient Edge Ensemble of Convolutional Neural Networks for Resource-Optimized Learning

Le Zhang, Onat Gungor, Flavio Ponzina, Tajana Rosing

Asia and South Pacific Design Automation Conference (ASPDAC) 2025

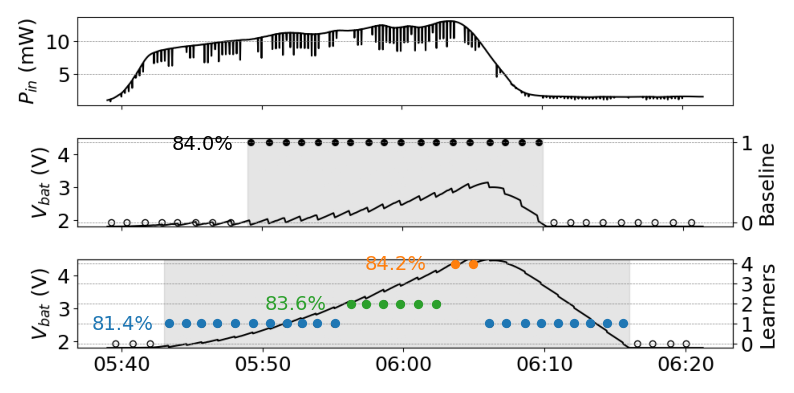

We propose E-QUARTIC, an energy-efficient edge ensembling framework that constructs CNN ensembles optimized for AI-based embedded systems, achieving higher accuracy than single-instance CNNs and existing edge solutions without additional memory overhead. Leveraging its multi-CNN architecture, E-QUARTIC also implements an energy-aware model selection strategy tailored for energy-harvesting AI environments.

E-QUARTIC: Energy Efficient Edge Ensemble of Convolutional Neural Networks for Resource-Optimized Learning

Le Zhang, Onat Gungor, Flavio Ponzina, Tajana Rosing

Asia and South Pacific Design Automation Conference (ASPDAC) 2025

We propose E-QUARTIC, an energy-efficient edge ensembling framework that constructs CNN ensembles optimized for AI-based embedded systems, achieving higher accuracy than single-instance CNNs and existing edge solutions without additional memory overhead. Leveraging its multi-CNN architecture, E-QUARTIC also implements an energy-aware model selection strategy tailored for energy-harvesting AI environments.

Efficient Multitask Learning on Resource-constrained Systems

Yubo Luo, Le Zhang, Zhenyu Wang, Shahriar Nirjon

International Conference on Embedded Wireless Systems and Networks (EWSN) 2024

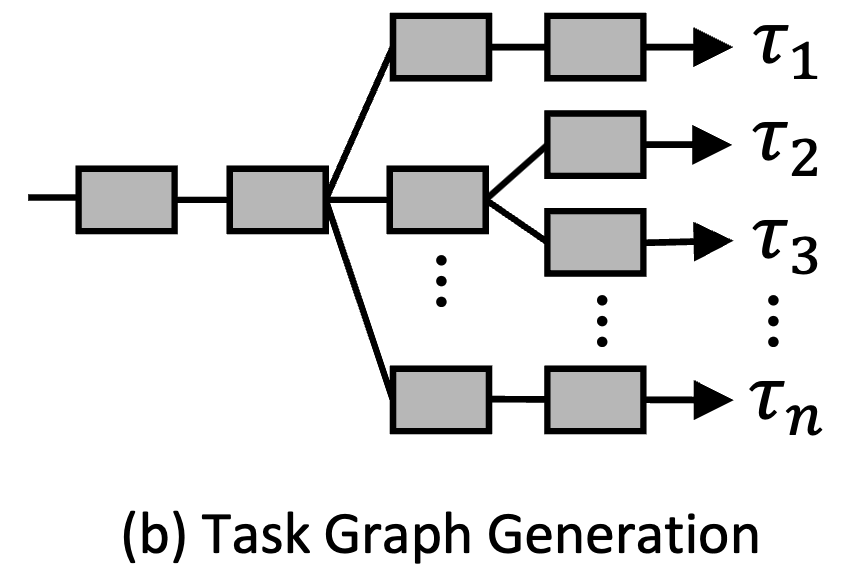

We introduce Antler, a multitask inference system that constructs a compact task graph by exploiting task affinities, optimizing the execution order to significantly reduce end-to-end inference time and energy usage. Antler leverages overlaps and dependencies among tasks to avoid redundant computations while maintaining accuracy comparable to state-of-the-art approaches.

Efficient Multitask Learning on Resource-constrained Systems

Yubo Luo, Le Zhang, Zhenyu Wang, Shahriar Nirjon

International Conference on Embedded Wireless Systems and Networks (EWSN) 2024

We introduce Antler, a multitask inference system that constructs a compact task graph by exploiting task affinities, optimizing the execution order to significantly reduce end-to-end inference time and energy usage. Antler leverages overlaps and dependencies among tasks to avoid redundant computations while maintaining accuracy comparable to state-of-the-art approaches.

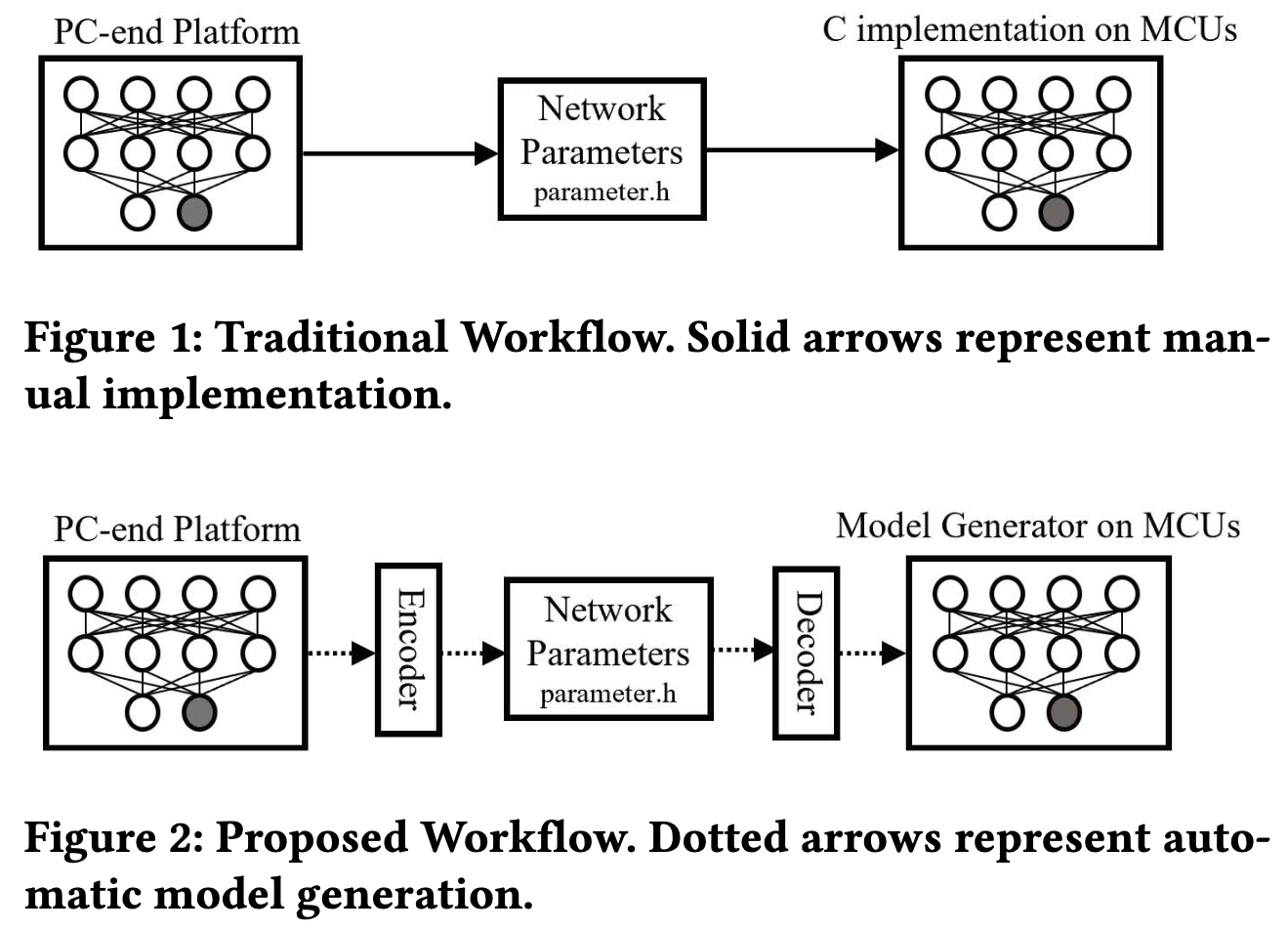

Demo Abstract: Capuchin: A Neural Network Model Generator for 16-bit Microcontrollers

Le Zhang, Yubo Luo, Shahriar Nirjon

ACM/IEEE International Conference on Information Processing in Sensor Networks (IPSN) 2022

We present a neural network model generator that automatically transfers parameters from pre-trained DNN or CNN models to 16-bit microcontrollers and implements on-device inference. This tool bridges the gap in efficiency and usability between development tools for 16-bit and 32-bit microcontrollers, significantly simplifying deep learning deployment on ultra-low-power devices.

Demo Abstract: Capuchin: A Neural Network Model Generator for 16-bit Microcontrollers

Le Zhang, Yubo Luo, Shahriar Nirjon

ACM/IEEE International Conference on Information Processing in Sensor Networks (IPSN) 2022

We present a neural network model generator that automatically transfers parameters from pre-trained DNN or CNN models to 16-bit microcontrollers and implements on-device inference. This tool bridges the gap in efficiency and usability between development tools for 16-bit and 32-bit microcontrollers, significantly simplifying deep learning deployment on ultra-low-power devices.